Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Le immagini servono solo come riferimento.

Consulta le specifiche del prodotto per i dettagli del prodotto.

Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Gli ordini superiori a $ 200 hanno diritto a un regalo in stile cinese in edizione limitata.

Gli ordini superiori a $ 1000 beneficiano di un'esenzione dalle spese di spedizione di $ 30.

Gli ordini superiori a $ 5000 beneficiano dell'esenzione dalle spese di spedizione e di transazione.

Queste offerte sono applicabili sia ai clienti nuovi che a quelli esistenti e sono valide dal 1 gennaio 2024 al 31 dicembre 2024.

Lattice

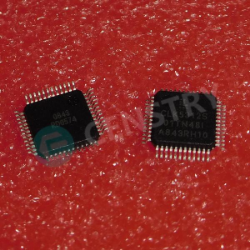

ISPPAC-CLK5312S-01TN48I datasheet

QFP-48

Ics orologio e timer

Invia la tua richiesta di preventivo adesso e prevediamo di fornirti un preventivo entro maggio 04, 2024. Effettua ora il tuo ordine e prevediamo di completare la transazione entro maggio 08, 2024. Ps: L'orario è secondo GMT+8:00.

Lattice

1540 PCS

SII9233ACTU-C .PDF

Lattice

11377 PCS

SII9187BCNU .PDF

Lattice

7799 PCS

SII9136CTU-3 .PDF

Lattice

310 PCS

SII163BCTG100 .PDF

2024-05-02

very fast thanks

2024-05-02

Fast shipping

2024-05-02

Goods arrived and work perfectly.

2024-05-01

impossible to find, except here.

2024-04-30

TRANSISTORS ARE GOOD

2024-04-27

Mercancía correcta. Envío rápido. Muy satisfecho.

2024-04-22

Censtry elec = Good company, happy business

2024-04-11

We highly recommend Pinewood Electronics Ltd and are looking forward to our next deal. Darren is very professional and our order was shipped promptly and the parts were good quality.

2024-03-21

Good supplier !i will buy it again ,Nice

2024-02-07

Very proffessional and reliable company. Was a pleasure for me to work with Mara.

Apprezziamo molto il tuo feedback. Per favore condividi la tua recensione più genuina.

*Effettua l'accesso al tuo account prima di pubblicare un commento